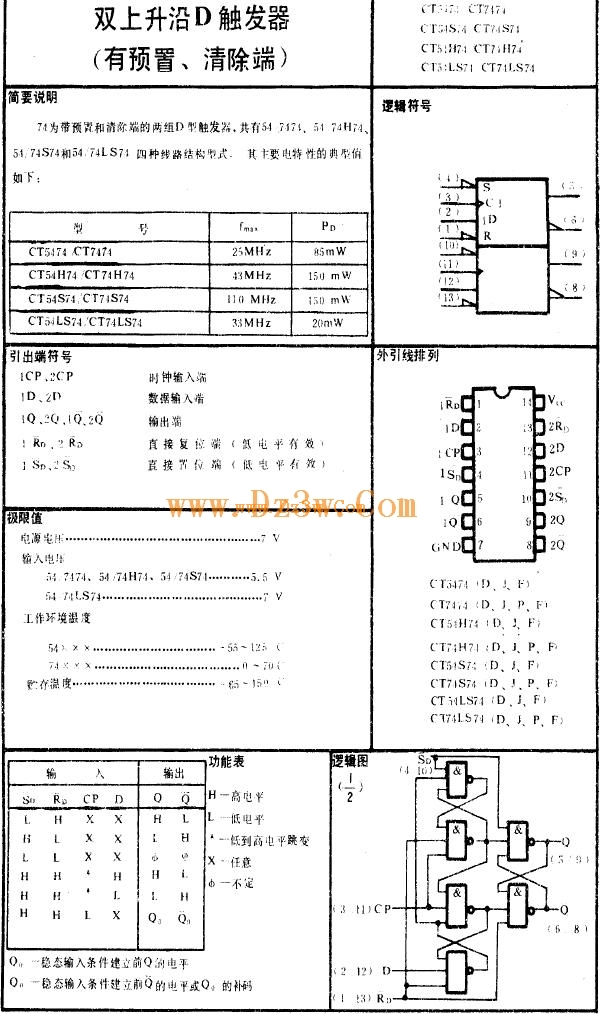

�������pD�|�l(f��)��74LS74�����Y��

74LS74��(n��i)���ɂ�������D�������pd�|�l(f��)����ÿ���|�l(f��)���Д�(sh��)��(j��)ݔ�루D������λݔ�루 ����(f��)λݔ�루

����(f��)λݔ�루 �����r�ݔ�루CP���͔�(sh��)��(j��)ݔ����Q��/Q����

�����r�ݔ�루CP���͔�(sh��)��(j��)ݔ����Q��/Q���� ��

�� �ĵ��ƽʹݔ���A(y��)�û���������c����ݔ��˵��ƽ�o�P(gu��n)����(d��ng)

�ĵ��ƽʹݔ���A(y��)�û���������c����ݔ��˵��ƽ�o�P(gu��n)����(d��ng) ��

�� ���oЧ�����ƽʽ���r�����Ͻ����r�gҪ���D��(sh��)��(j��)��CP�������������͵�ݔ���ˡ�

���oЧ�����ƽʽ���r�����Ͻ����r�gҪ���D��(sh��)��(j��)��CP�������������͵�ݔ���ˡ�

74ls74���ܱ�:

ݔ ��

| ݔ ��

| ||||

SD

| RD

| CP

| D

| Qn��1

| Qn��1

|

0

| 1

| ×

| ×

| 1

| 0

|

1

| 0

| ×

| ×

| 0

| 1

|

0

| 0

| ×

| ×

| φ

| φ

|

1

| 1

| ↑

| 1

| 1

| 0

|

1

| 1

| ↑

| 0

| 0

| 1

|

1

| 1

| ↓

| ×

| Qn

| Qn

|

��

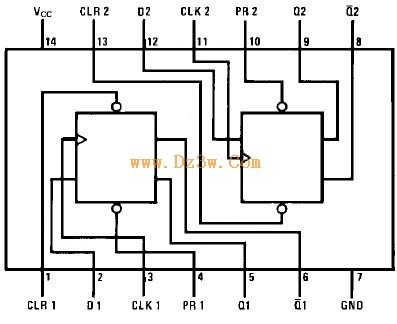

�D1 74ls74���_�D

��

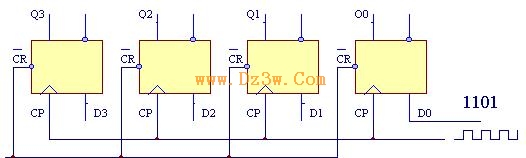

��74LS74��(g��u)��4λ�Ĵ���

һ��D�|�l(f��)���Ɍ��F(xi��n)һλ���M��(sh��)�Ĵ惦����ˑ�(y��ng)����4��D�|�l(f��)�����F(xi��n)4λ�Ĵ���������Ҫ���F(xi��n)��λ�Ĵ棬4��D�|�l(f��)��֮�g��(y��ng)�(li��n)�ӡ�

��1�������ڈD2���������(y��ng)��(li��n)������(g��u)�ɿɌ��F(xi��n)���벢�������봮�������봮�������벢���Ķ����λ�Ĵ档���D�Ӻ��·��

(2) D3 D2 D1 D0�քe��߉�_�P(gu��n)��Q3 Q2 Q1 Q0�Ӱl(f��)����O�ܣ�

(3) �����㣻

(4) ������Ҫ���F(xi��n)����(y��ng)���ܣ��^��Y(ji��)���������������^�̡�

���벢����

ʹ��(sh��)��(j��)ݔ���D3D2D1D0=1011���oCP��ݔ��һ�������}�_���^��Q3Q2Q1Q0�l(f��)����O�ܵĠ�B(t��i)�������Y(ji��)��������С�

���봮����

ʹ��(sh��)��(j��)ݔ���D3D2D1D0=1011���oCP��ݔ��4�������}�_���^��Q3�˰l(f��)����O�ܵĠ�B(t��i)�����Y(ji��)�������6�С�

���벢����

ʹ��(sh��)��(j��)ݔ���D0�քe��1011��ͬ�rͨ�^�oCP��ݔ�������}�_��D0�˵�4 ����(sh��)��(j��)����Ĵ������^��Q3Q2Q1Q0�˰l(f��)����O�ܵĠ�B(t��i)�����Y(ji��)��������С�

���봮����

ʹ��(sh��)��(j��)ݔ���D0�քe��1011��ͬ�rͨ�^�oCP��ݔ�������}�_����D0�˵�4 ����(sh��)��(j��)����Ĵ�������CP��ݔ��8���}�_���^��Q3�˰l(f��)����O�ܵĠ�B(t��i)�����Y(ji��)�������2�С���

��

���벢����

| D3D2D1D0=1011

| 1��CP�}�_

| Q3Q2Q1Q0=

| �Y(ji��)Փ��

|

���봮��

| D3D2D1D0=1011

| 4��CP�}�_

| Q3=

| �Y(ji��)Փ

|

���벢��

| D3=1011

| 4��CP�}�_

| Q3Q2Q1Q0=

| �Y(ji��)Փ

|

���봮��

| D3=1011

| 8��CP�}�_

| Q3=

| �Y(ji��)Փ

|

��

�D2

![IC�]ُ�W(w��ng)���Ԫ��Ʒ�|(zh��)����](/static/img/950.jpg)